# **ITRS 2.0 - More Moore update**

Mustafa Badaroglu mustafab@qti.qualcomm.com

On behalf of More Moore Focus Team – Device, Memory, Litho, Interconnect, FEP, Metrology TWGs

July 12, 2015 ITRS summer meeting, Stanford Univ., Palo Alto, CA, USA

Work in Progress – Not for Distribution More Moore FT, ITRS summer meeting, Stanford Univ., Palo Alto, CA, USA, July 11-12, 2015 1

## **ITRS 2.0 - More Moore Mission**

Provide physical, electrical and reliability requirements for logic and memory technologies to sustain More Moore (PPAC: power, performance, area, cost) scaling for big data, mobility, and cloud (IoT and server) applications and

Forecast logic and memory technologies (15 years) in main-stream/high-volume manufacturing (HVM)

# **Cloud and mobile computing drive More Moore**

- Device-interconnect tech should meet microserver and mobile computing needs

- Edge computing requires additional functionality for increased consumer value (e.g. motion processor, neural processor unit, etc)

- 2.5D integration to scale memory bandwidth / power and latency

#### Work in Progress – Not for Distribution

## **More Moore computational drivers**

E----

| Enablers:<br>Multi-core pr<br>MPU, GPU, f<br>2.5D/3D inte<br>Wide-IO for r | FPGA in single chip<br>gration | Enablers:<br>Heterogenous integration<br>Massive parallelism – (many-core)<br>Cognitive & probabilistic computing<br>Logio-in memory<br>Cloud computing<br>Connectivity of everything<br>Multi-thread applications<br>Real-time reconfigurability<br>Visually rich gaming & browsing<br>HD streaming<br>Data accessible everywhere/time | Location awareness & tracking<br>Emotion/environment recognition<br>HD-3D conferencing and streaming<br>Real-time rendering<br>Personal health-care |  |  |  |

|----------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                            |                                |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                     |  |  |  |

| PC                                                                         | Internet                       | Multimedia &<br>Mobile internet                                                                                                                                                                                                                                                                                                         | Virtual reality and<br>location awareness                                                                                                           |  |  |  |

| 1990                                                                       | 2000                           | 2010                                                                                                                                                                                                                                                                                                                                    | 2020                                                                                                                                                |  |  |  |

| 100M+ units                                                                | IB+ units                      | 10B+ units                                                                                                                                                                                                                                                                                                                              | 100B+ units                                                                                                                                         |  |  |  |

| Source: Morg                                                               | an Stanley Research            | ,                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                     |  |  |  |

#### Work in Progress – Not for Distribution

# Application KPIs and PPAC scaling for More Moore

| · ···································· |

|----------------------------------------|

| 2 j                                    |

| 💆 🖳 😫 🧕                                |

| 👲 🗉 🙆                                  |

|                                        |

|                                        |

### Data/compute servers

- KPI = More performance at iso power density

- Constraints = Thermal, energy budget

- Edge computing

- KPI = More performance & functionality at iso power and cost

- Constraints = Cost, battery, increased leakage in parallel HW

- Smart sensors

- KPI = Reduced leakage and variability at near-Vt

- Constraints = System form factor, cost, and security

- More Moore platform for node-to-node PPAC value

- Performance: >25-30% more fmax @ iso power

- Power: >50% less energy / switching at given performance

- Area: >50% area reduction

- Cost: <25% wafer cost ~30% less cost for same function

# **TTRS**

#### Work in Progress – Not for Distribution

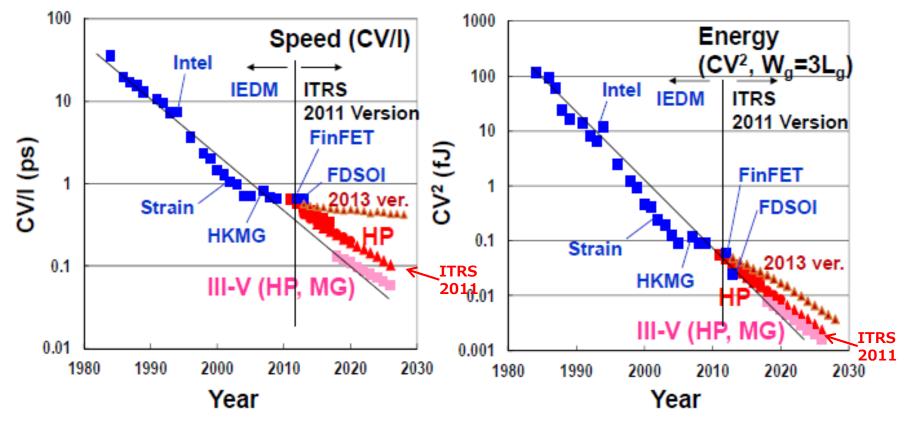

# Performance saturates in conventional scaling

#### Saturated performance improvement trend, 2013 ITRS

Source ; Prof. Hiramoto, Tokyo Univ.

Work in Progress – Not for Distribution

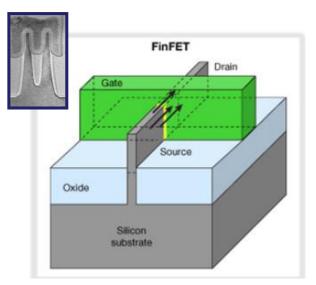

# **Device architecture evolution to scale CPP**

### finFET 2011-2019 Lgate/finwidth=3 Weff, SCE

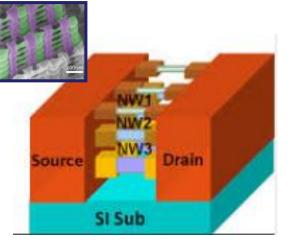

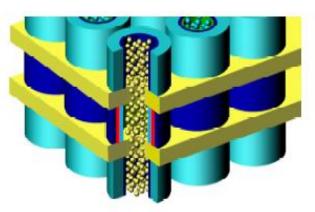

Lateral GAA (gate-all-around) 2018-2024 Lgate/NWD=2 Scale Lgate ~ power reduction

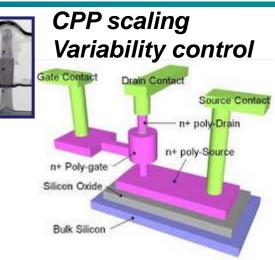

Vertical GAA 2022-2028 Lgate/NWD=2 Variability control, Rext

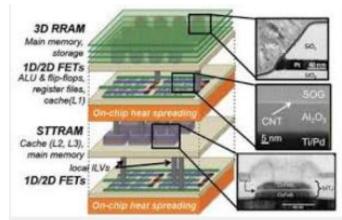

Monolithic 3D (M3D) 2024-beyond Lgate/NWD=2 Functional scaling

Work in Progress – Not for Distribution

# LGAA and VGAA FEP and metrology challenges

Vertical GAA or NW

Stacked lateral GAA or NW

S-G. Hur, Samsung

Kuhn, Intel, 2012

Stacked NW and GAA structures bring new FEP process challenges

- Conformality

- Integrity

- Reliability

- Controls

- 3D metrology for sub-10nm

- Defectivity

**ALRS**

Work in Progress – Not for Distribution Yield

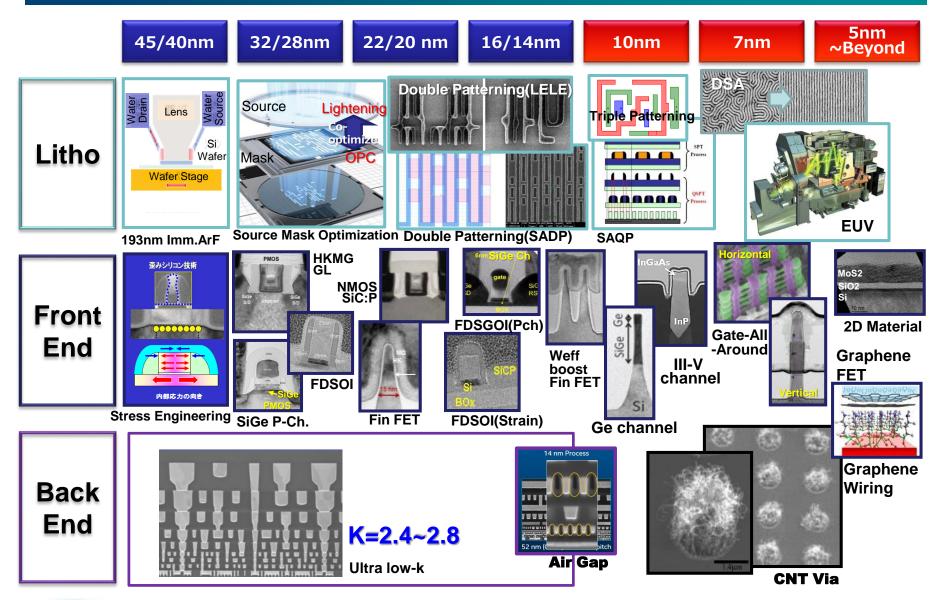

### **Technology Roadmap Landscape**

Work in Progress - Not for Deputtesy: Yuzo Fukuzaki - Sony Corporation

# Main scaling focus & performance boosters

|                                           | H                      |                        | 200                     | n                       | 1                                 | <u>10 m</u>                       |                                            |                                            |

|-------------------------------------------|------------------------|------------------------|-------------------------|-------------------------|-----------------------------------|-----------------------------------|--------------------------------------------|--------------------------------------------|

| YEAR OF PRODUCTION                        | 2015                   | 2016                   | 2018                    | 2020                    | 2022                              | 2024                              | 2026                                       | 2028                                       |

| Logic device technology naming            | P70M52                 | P52M36                 | P42M24                  | P32M16                  | P24M12                            | P24M12V1                          | P24M12V2                                   | P24M12V3                                   |

| Logic industry "Node Range" Labeling (nm) | "16/14"                | "11/10"                | "8/7"                   | "6/5"                   | "4/3"                             | "3/2.5"                           | "2/1.5"                                    | "1/0.75"                                   |

| Node production years                     | 3                      | 3                      | 3                       | 3                       | 3                                 | 3                                 | 3                                          | >3                                         |

| Device structure options                  | finFET<br>FDSOI        | finFET<br>FDSOI        | finFET<br>LGAA          | finFET<br>LGAA<br>VGAA  | VGAA, M3D                         | VGAA, M3D                         | VGAA, M3D                                  | VGAA, M3D                                  |

| DEVICE ARCHITECTURE & MODULES             |                        |                        |                         |                         |                                   |                                   |                                            |                                            |

| N-channel                                 | Si                     | sSi                    | sSi, Ge                 | sSi, sGe, IIIV          | sSi, sGe, IIIV                    | sSi, sGe, IIIV                    | sSi, sGe, IIIV                             | sSi, sGe, IIIV                             |

| P-channel                                 | Si                     | Si,SiGe                | Si,SiGe                 | Si,SiGe                 | Ge                                | Ge                                | Ge                                         | Ge                                         |

| DEVICE PERFORMANCE BOOSTERS               |                        |                        |                         |                         |                                   |                                   |                                            |                                            |

| Main performance booster                  | SCE<br>finHeight<br>Vt | SCE<br>finHeight<br>Vt | Parasitics<br>finHeight | Parasitics<br>finHeight | Low Vdd<br>3D                     | Low Vdd<br>3D                     | Low Vdd<br>3D                              | Low Vdd<br>3D                              |

| Scaling focus                             | Perf                   | Power                  | Power                   | Power                   | Function                          | Function                          | Function                                   | Function                                   |

| Transport scheme                          | DD                     | Quasi<br>Ballistic     | Quasi<br>Ballistic      | Ballistic               | Ballistic<br>TFET, JFET,<br>NCMOS | Ballistic<br>TFET, JFET,<br>NCMOS | Ballistic<br>TFET, JFET,<br>NCMOS,<br>Spin | Ballistic<br>TFET, JFET,<br>NCMOS,<br>Spin |

- Added new node naming nomenclature (e.g. P70M52) since pitch scaling is not directly representing node itself

- 2014-2018 (N14, N10) focus on SCE, Weff scaling through cell height reduction

- 2018-2022 (N7 and N5) focus on parasitics, Weff efficiency, DTCO

- 2022-2030 (N3 and beyond) focus on ultra low-Vdd and 3D functional integration

#### Work in Progress – Not for Distribution

# Inflection (2018) - Lateral GAA transition

- Benefits

- Strong short channel control high beneficial in loaded cells

- Can use the finFET baseline as process starting point

- Technology challenges

- Undercut control during channel formation

- HKMG integration surrounding NW

- Parasitic channel

- Stressor to mobility transfer

- Conformal deposition

- Design challenges

- Self-heating

- Enabling SoC components ESD, IO

- Variability

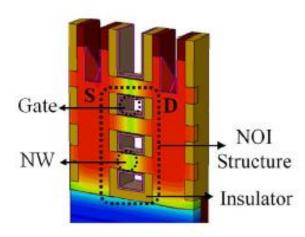

# Inflection (2022) - Vertical GAA transition

- Benefits

- Strong short channel control high beneficial in loaded cells

- No need for isolation

- Reduced SRAM area

- Technology challenges

- Etch control

- HKMG integration surrounding NW easier compared to finFET

- Bottom contact formation

- Bottom junction engineering

- Device/Design challenges

- Gate density

- Same as lateral nanowire

- 3D stdcell design & port access difficulties

- Place & route

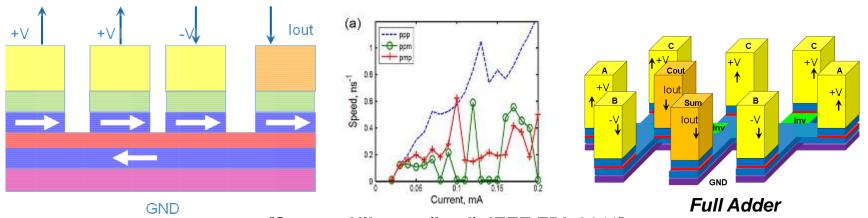

# Inflection (2022) - monolithic-3D transition

- Benefits

- Strong short channel control high beneficial in loaded cells

- No need for isolation

- Active devices in the interconnect

- Ability to scale drive in the vertical direction

- P-N separation across tuers

- Technology challenges

- Same as vertical nanowire

- Temperature budget

- Channel growth

- Low-temperature activation

- Device/Design challenges

- New functions and architectures

- Same as vertical nanowire

- 3D stdcell design & port access difficulties

- Less number of layers across tiers

- Place & route

#### Work in Progress – Not for Distribution

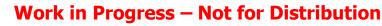

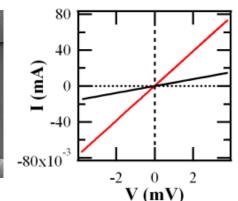

## Lgate slow-down forcing alt. transport

TFET

[Source: Yeung (UCB), SISPAD 2012]

[Source: Thean (imec), ITF 2013]

#### Work in Progress – Not for Distribution

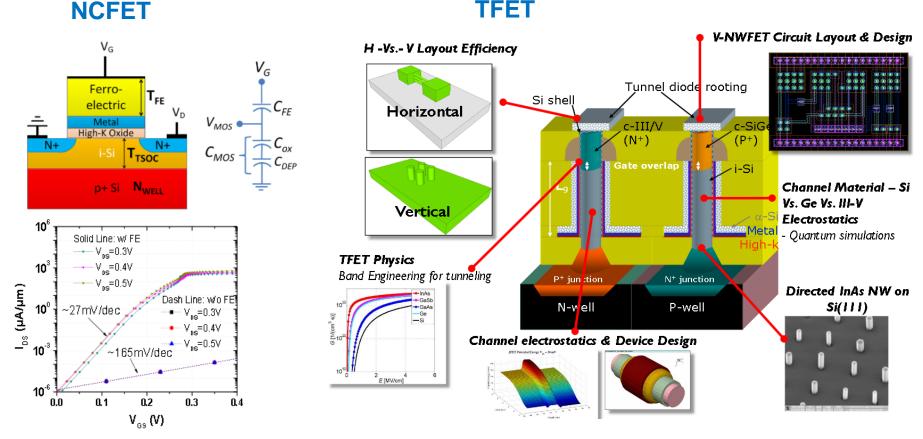

### Other transport options

<n-channel I-MOS>

[Source: Gopalakrishnan (Stanford U.), IEDM 2002]

**STMG**

[Source: Nikonov (Intel), IEEE EDL 2011]

#### Work in Progress – Not for Distribution

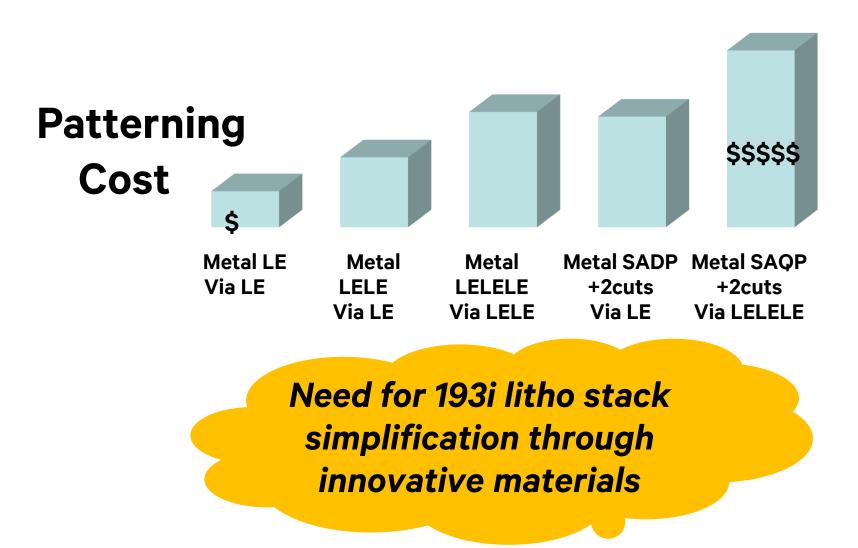

### **193i multi-patterning cost explosion**

Work in Progress – Not for DistributionMore Moore FT, ITRS summer meeting, Stanford Univ., Palo Alto, CA, USA, July 11-12, 201516

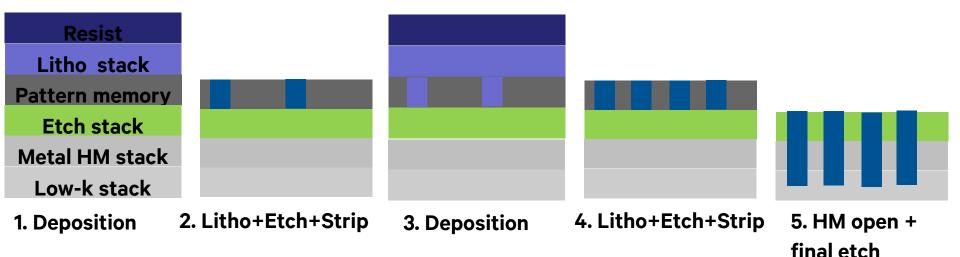

# EUV - simplifying stack and saving steps

# 193i LELE metal patterning

# EUV SE metal patterning

Pros

- Simplified stack

- Avoiding CDU and OVL seen in MPT

- Less # of depo, litho, etch steps

Cons

Need improvements in resists for productivity and better LER

#### Work in Progress – Not for Distribution

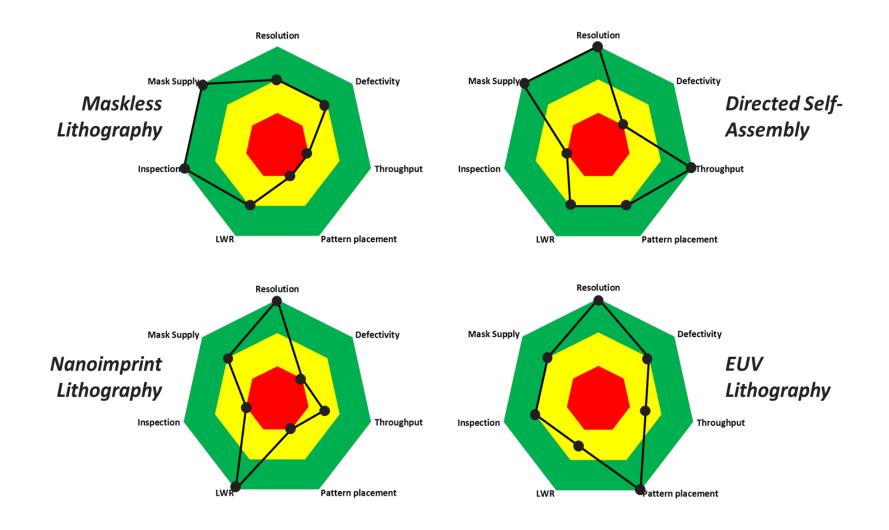

## Pros/cons of patterning approaches

#### **Courtesy: Mark Neisser - Sematech**

### Work in Progress – Not for Distribution

## <u>Interconnect – new barriers, conductors</u>

| YEAR OF PRODUCTION                                            | 2015            | 2016                                  | 2018                                  | 2020                                                   | 2022                                                   | 2024                                                   | 2026                                                   | 2028                                                   |

|---------------------------------------------------------------|-----------------|---------------------------------------|---------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| Logic device technology naming                                | P70M52          | P52M36                                | P42M24                                | P32M16                                                 | P24M12                                                 | P24M12V1                                               | P24M12V2                                               | P24M12V3                                               |

| Logic industry "Node Range" Labeling (nm)                     | "16/14"         | "11/10"                               | "8/7"                                 | "6/5"                                                  | "4/3"                                                  | "3/2.5"                                                | "2/1.5"                                                | "1/0.75"                                               |

| Node production years                                         | 3               | 3                                     | 3                                     | 3                                                      | 3                                                      | 3                                                      | 3                                                      | >3                                                     |

| Device structure options                                      | finfet<br>FdSOI | finFET<br>FDSOI                       | finFET<br>LGAA                        | finFET<br>LGAA<br>VGAA                                 | VGAA, M3D                                              | VGAA, M3D                                              | VGAA, M3D                                              | VGAA, M3D                                              |

| INTERCONNECT TECHNOLOGY                                       |                 |                                       |                                       |                                                        |                                                        |                                                        |                                                        |                                                        |

| Conductor                                                     | Cu              | Cu                                    | Cu                                    | Cu<br>Silicides<br>Carbon<br>Collective<br>Excitations | Cu<br>Silicides<br>Carbon<br>Collective<br>Excitations | Cu<br>Silicides<br>Carbon<br>Collective<br>Excitations | Cu<br>Silicides<br>Carbon<br>Collective<br>Excitations | Cu<br>Silicides<br>Carbon<br>Collective<br>Excitations |

| Number of wiring layers                                       | 10              | 11                                    | 12                                    | 13                                                     | 15                                                     | 17                                                     | 19                                                     | 21                                                     |

| Barrier metal - intermediate wire (tight pitch)               | Ta(N)           | Ta(N), Mn(N)                          | Ta(N), Mn(N)                          | Ta(N),<br>Mn(N), SAM                                   |

| Barrier thickness - intermediate wire                         |                 |                                       |                                       |                                                        |                                                        |                                                        |                                                        |                                                        |

| Inter-metal dielectrics (IMD) and k value - intermediate wire | SiCOH<br>(2.55) | SiCOH (2.40-<br>2.55)<br>Airgap (1.0) | SiCOH (2.20-<br>2.55)<br>Airgap (1.0) | SiCOH (2.20-<br>2.55)<br>Airgap (1.0)<br>MOF, COF      | 2.55)                                                  | 2.55)                                                  | SiCOH (2.00-<br>2.55)<br>Airgap (1.0)<br>MOF, COF      | SiCOH (2.00-<br>2.55)<br>Airgap (1.0)<br>MOF, COF      |

Work in Progress – Not for Distribution

# **Enablers for resistance reduction**

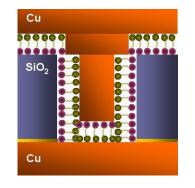

### **Ultrathin Cu Barrier Layers**

(1) SAM(Self-assembled Monolayer)

NH2(CH2)3Si (OCH3)3 Source: Arantxa Maestre Caro, Intel Corp. at IMEC

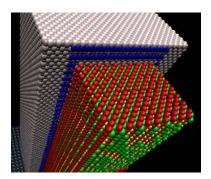

### **Alternative Conductors**

# Proposals from ERM TWG

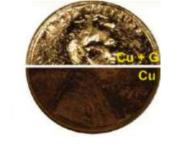

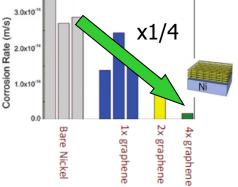

### (2) Graphene barrier

Oxidation and corrosion resistance

Chen et al., ACS Nano 5, 1321 (2011) Prasai et al., ACS Nano DOI: 10.1021/nn203507y (2011)

(3) Graphene

Kondo et al., IITC2013

### (4) Other candidates

- CNT Interconnects

- CNT-Cu composites

9.1 μΩcm at 6 μm length and 4 μm width Work in Progress – Not for Distribution More Moore FT, ITRS summer meeting, Stanford Univ., Palo Alto, CA, USA, July 11-12, 2015

20

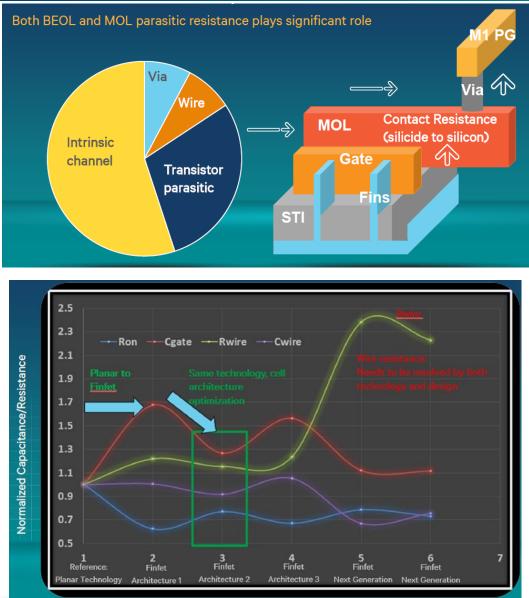

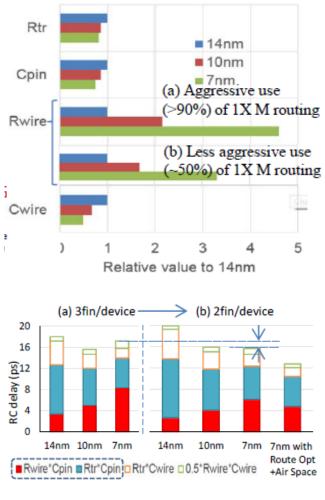

## Transistor drive needs to be optimized

Source: SC Song (Qualcomm), VLSI 2015

Work in Progressereel Joefzioglis (Qbalcomm), ICICDT 2015

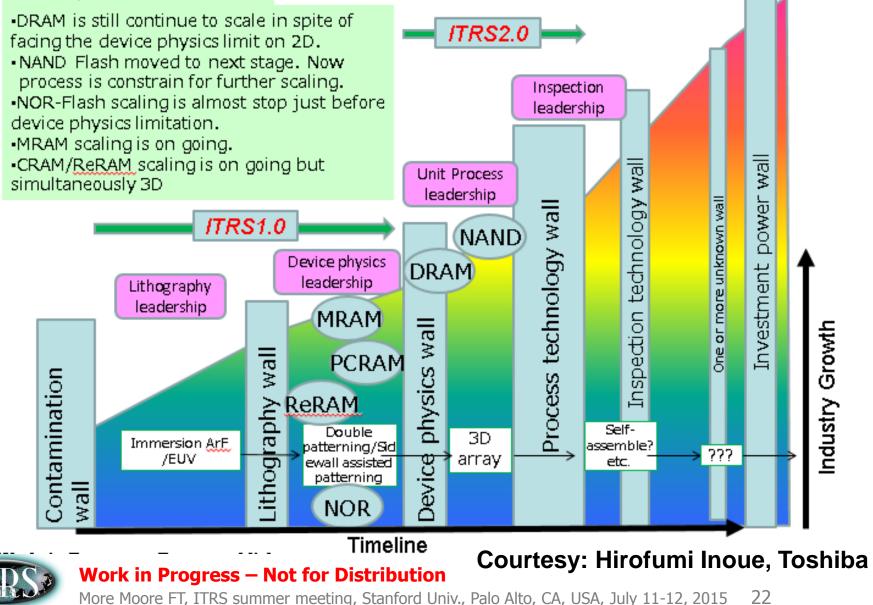

## Memory scaling wall image

#### Memory status 0n 2015

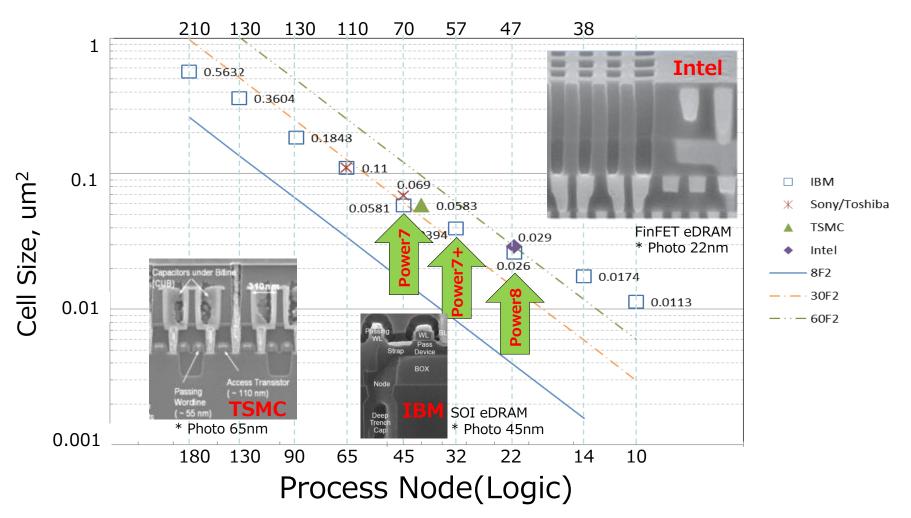

### eDRAM size trend – MRAM potential >2019 for L4

eDRAM Half pitch(real F for cell design) = same F/Node definition as DRAM

Courtesy: Yuzo Fukuzaki, Sony Corp.

#### Work in Progress – Not for Distribution

# Conclusions

- Mobile computing, big data, cloud (microserver, IoT) will continue to drive low power technology and design

- New materials needed to resolve the interconnect bottleneck but lack of disruptive solutions, more design solutions for mitigation

- Memory scaling key for the server market handling big data

- NVM scaling requires new memory technologies (e.g. MRAM, RRAM) and embedded memories for IoT

- More Moore ITRS2.0 focusing on requirements and mitigation approaches/gaps to sustain