### Extending our calculations to a collection of nodes

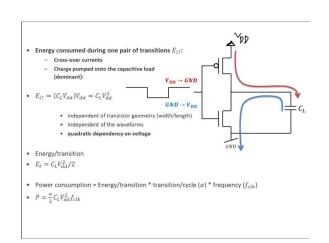

· Average energy dissipated per computation cycle for one circuit node

$$E_{chk} = \frac{\alpha_k}{2} E_{ch\,cyc\,k} = \frac{\alpha_k}{2} C_k U_{dd}^2$$

Average energy dissipated per computation cycle in a voltage domain of K nodes

$$E_{ch} = \sum_{k=1}^{K} E_{ch\,k} = U_{dd}^2 \sum_{k=1}^{K} \frac{\alpha_k}{2} C_k$$

# Node activity (aka switching activity)

- Fact: Not all nodes within a (sub)circuit do change state at the same rate.

- Definition

A node's activity  $\alpha_k$  indicates how many times per computation cycle node k switches from one logic state to the opposite one when averaged over many computation cycles.

- Examples:

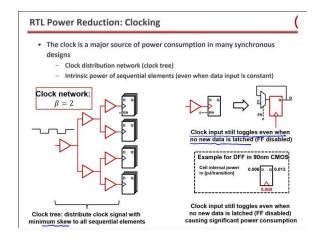

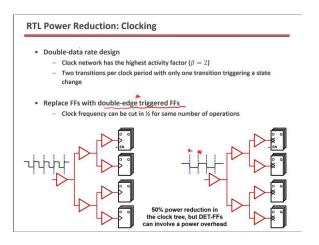

- Ungated clock in single-edge-triggered clocking:  $\alpha_k=2$

- Ungated clock in dual-edge-triggered clocking:  $lpha_k=1$

- Output of a T-type Flip-Flop if permanently enabled:  $lpha_k=1$

- Output of a D-type Flip-Flop fed with random data:  $\alpha_k = 1/2$

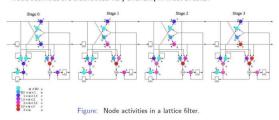

### Impact of Glitching

- In a synchronous (single-edge triggered) circuit, the activity factor of each node should never rise above  $\alpha_k=1/2$

- Reality: activity factors up to 6 or more can be observed:

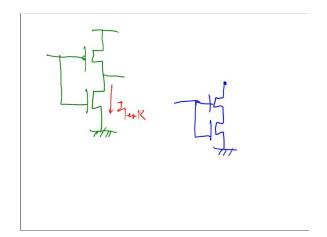

- Increased activity due to glitches: signals reconverge after having propagated along paths of markedly different depths

- Glitching explains why the isomorphic architecture often dissipates more (dynamic) energy than more sophisticated architectures do.

- Activity caused by glitches is very difficult to predict (depends heavily on timing)

- Analytical prediction almost impossible

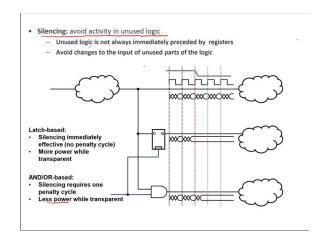

Node activities are distributed very unevenly in most circuits.

Activity increases with the number of preceding logic stages (increased glitching)

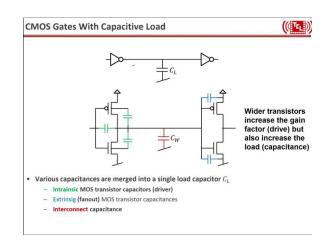

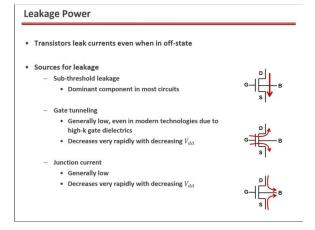

- Power consumption is divided into

- Net switching power

- Internal power

- Internal power depends on actual input values

- Power is consumed even if output does not change

- Library files: internal energy characterization for each cell at given supply voltage

- Internal energy (cross-current, switching) per change in each input and output (as functions of input slope  $t_{rf}$  and output load  $\it C$ )

- Contribution to capacitance of the connected net (input/output load)

$C = C_{AOI}^Z + C_{net} + C_{INV}^A$

#### What about the activity factor(s)?

Fixed activity:

Assume a constant activity factor for all nodes in the circuit

Very rough estimate and highly inaccurate

Statistical power analysis:

Assumes a given toggle activity at the input and propagates the activity throughout the circuit using statistical models of the gates

- Does not account for correlation between signal values

- No accounting for glitching activity

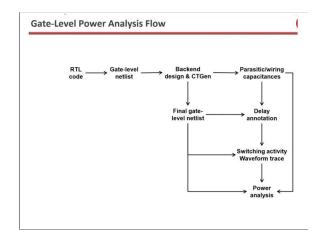

- Simulation based:

Obtains toggle statistics from gate level simulations

- Most accurate method

- Slow

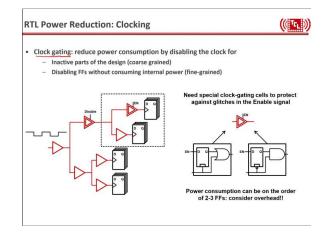

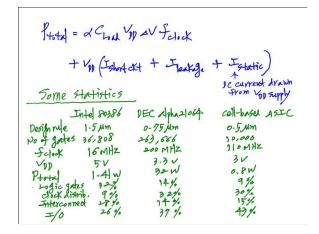

• The clock is a major source of power consumption in many synchronous designs

J. Rabaey: Power figures from sever microprocessors and DSPs

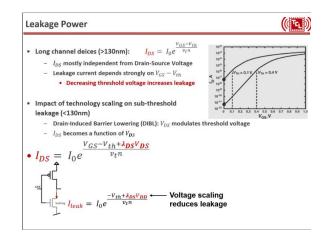

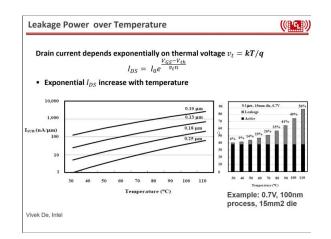

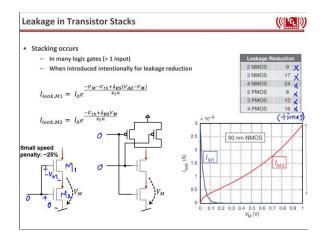

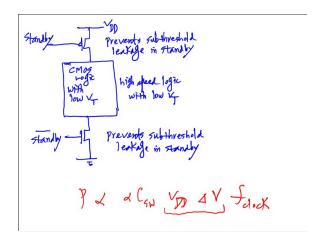

### **Threshold Voltage Selection**

- Modern process technologies support devices with different threshold voltages

- Typically three flavors: low-VT, standard-VT, high-VT

- Often all three flavors can be mixed in the same design

- VT-selection: tradeoff between speed and leakage

$$t_{pd} = \frac{t_{OX}}{\mu \varepsilon_{OX}} \frac{L}{W} C_L \frac{V_{DD}}{(V_{DD} - V_{th})^{\alpha}}$$

$$I_{leak} = I_0 e^{\frac{-V_{th} + \lambda_{DS} V_{DS}}{v_t n}}$$

• Example: 55nm process

Delay Leakage

HVT **D**-

20ps 30nW

SVT 1 16ps 60nW

LVT

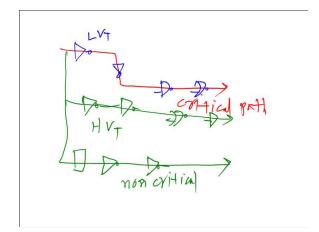

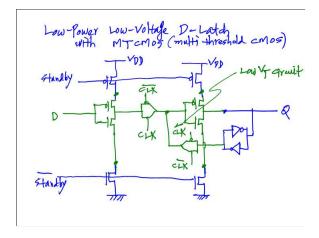

# Multi-VT Design

- Design tradeoff when choosing a VT flavor:

- Less leakage (high-VT) increases delay and vice versa

- Threshold voltage types can often be mixed

High-VT cells are used in all other paths

Caveat: can be very problematic for near-VT or sub-VT design: path delays scale very differently

Methodology:

Either done by replacing non-critical cells in the backend OR already during synthesis by providing multiple libraries (HVT/SVT and LVT)

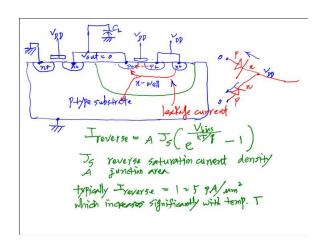

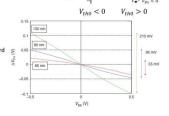

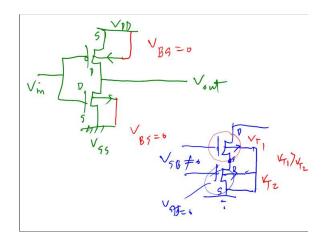

# **Body Bias Modulates Threshold Voltage**

((111))

- Body of the transistor is often connected to the source (no body bias)

- Introducing a body bias modulates threshold voltage

- Forward Body Bias (FBB): increases threshold voltage

Reverse Body Bias (RBB): reduces threshold voltage

- Effect of body bias decreases for

- technologies below 100nm FBB is limited to ~300mV to avoid

- operating junction diodes in forwardirection

Givan Sspec ( T < Tspec)

minimize power

so ling as meeting spees

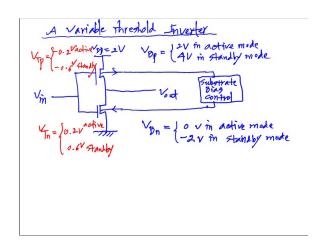

StrA with high by everywhere

But for timing critical paths,

lower by

Further, you can also adjust you

& play with by (bias voltage programing)

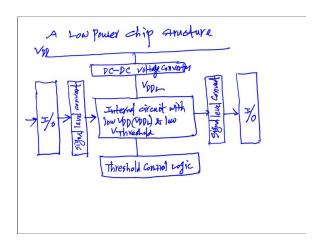

multiple VDD, multiple by, exter.